CLA40P1200FC

High Efficiency Thyristor

VRRM

= 2x 1200 V

I TAV

=

40 A

VT

=

1.19 V

Phase leg

Part number

CLA40P1200FC

Backside: isolated

2

1

4

5

3

Features / Advantages:

Applications:

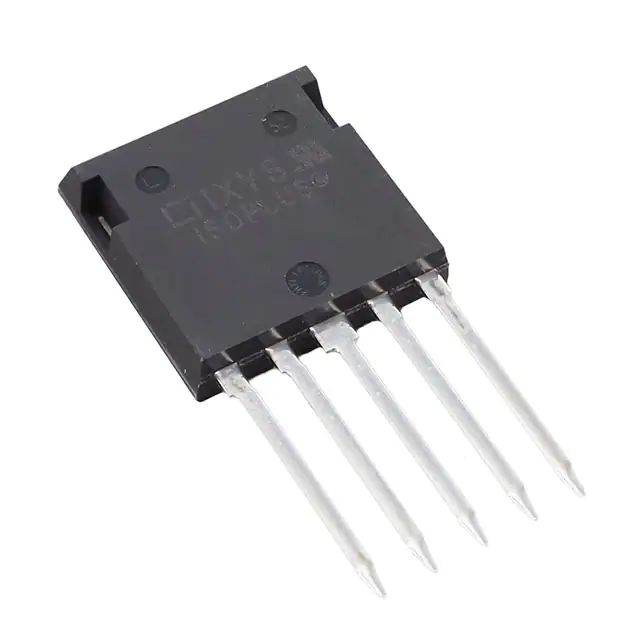

Package: i4-Pac

● Thyristor for line frequency

● Planar passivated chip

● Long-term stability

● Line rectifying 50/60 Hz

● Softstart AC motor control

● DC Motor control

● Power converter

● AC power control

● Lighting and temperature control

● Isolation Voltage: 3000 V~

● Industry convenient outline

● RoHS compliant

● Epoxy meets UL 94V-0

● Soldering pins for PCB mounting

● Backside: DCB ceramic

● Reduced weight

● Advanced power cycling

Disclaimer Notice

Information furnished is believed to be accurate and reliable. However, users should independently

evaluate the suitability of and test each product selected for their own applications. Littelfuse products are not designed for,

and may not be used in, all applications. Read complete Disclaimer Notice at www.littelfuse.com/disclaimer-electronics.

IXYS reserves the right to change limits, conditions and dimensions.

© 2019 IXYS all rights reserved

Data according to IEC 60747and per semiconductor unless otherwise specified

20191202d

�CLA40P1200FC

Ratings

Thyristor

Conditions

Symbol

VRSM/DSM

Definition

max. non-repetitive reverse/forward blocking voltage

TVJ = 25°C

VRRM/DRM

max. repetitive reverse/forward blocking voltage

TVJ = 25°C

1200

I R/D

reverse current, drain current

VT

forward voltage drop

TVJ = 25°C

50

µA

4

mA

TVJ = 25°C

1.25

V

1.49

V

1.19

V

IT =

40 A

IT =

80 A

IT =

40 A

IT =

80 A

I T(RMS)

RMS forward current

180° sine

VT0

threshold voltage

rT

slope resistance

R thJC

thermal resistance junction to case

TVJ = 125 °C

for power loss calculation only

thermal resistance case to heatsink

total power dissipation

I TSM

max. forward surge current

value for fusing

V

TVJ = 125°C

TC = 95 °C

RthCH

max. Unit

1300

V

VR/D = 1200 V

average forward current

Ptot

typ.

VR/D = 1200 V

I TAV

I²t

min.

1.50

V

T VJ = 150 °C

40

A

63

A

TVJ = 150 °C

0.86

V

7.9

mΩ

0.8 K/W

0.2

K/W

TC = 25°C

150

W

t = 10 ms; (50 Hz), sine

TVJ = 45°C

650

A

t = 8,3 ms; (60 Hz), sine

VR = 0 V

700

A

t = 10 ms; (50 Hz), sine

TVJ = 150 °C

555

A

t = 8,3 ms; (60 Hz), sine

VR = 0 V

595

A

t = 10 ms; (50 Hz), sine

TVJ = 45°C

2.12 kA²s

t = 8,3 ms; (60 Hz), sine

VR = 0 V

2.04 kA²s

t = 10 ms; (50 Hz), sine

TVJ = 150 °C

1.54 kA²s

t = 8,3 ms; (60 Hz), sine

VR = 0 V

CJ

junction capacitance

VR = 400 V f = 1 MHz

TVJ = 25°C

PGM

max. gate power dissipation

t P = 30 µs

T C = 150 °C

1.48 kA²s

25

t P = 300 µs

pF

10

W

5

W

0.5

W

PGAV

average gate power dissipation

(di/dt) cr

critical rate of rise of current

TVJ = 150 °C; f = 50 Hz

repetitive, IT = 120 A

t P = 200 µs; di G /dt = 0.3 A/µs;

(dv/dt)cr

critical rate of rise of voltage

V = ⅔ VDRM

VGT

gate trigger voltage

VD = 6 V

TVJ = 25 °C

1.5

TVJ = -40 °C

1.6

V

I GT

gate trigger current

VD = 6 V

TVJ = 25 °C

50

mA

TVJ = -40 °C

80

mA

VGD

gate non-trigger voltage

TVJ = 150°C

0.2

V

I GD

gate non-trigger current

3

mA

IL

latching current

TVJ = 25 °C

125

mA

IG =

0.3 A; V = ⅔ VDRM

non-repet., I T =

150 A/µs

40 A

500 A/µs

1000 V/µs

TVJ = 150°C

R GK = ∞; method 1 (linear voltage rise)

VD = ⅔ VDRM

tp =

10 µs

IG =

0.3 A; di G /dt =

V

0.3 A/µs

IH

holding current

VD = 6 V R GK = ∞

TVJ = 25 °C

100

mA

t gd

gate controlled delay time

VD = ½ VDRM

TVJ = 25 °C

2

µs

tq

turn-off time

IG =

0.3 A; di G /dt =

VR = 100 V; I T =

0.3 A/µs

40A; V = ⅔ VDRM TVJ =125 °C

di/dt = 10 A/µs dv/dt =

IXYS reserves the right to change limits, conditions and dimensions.

© 2019 IXYS all rights reserved

200

µs

20 V/µs t p = 200 µs

Data according to IEC 60747and per semiconductor unless otherwise specified

20191202d

�CLA40P1200FC

Package

Ratings

i4-Pac

Symbol

I RMS

Definition

Conditions

RMS current

per terminal

min.

TVJ

virtual junction temperature

T op

operation temperature

Tstg

storage temperature

-40

typ.

max.

70

Unit

A

-40

150

°C

-40

125

°C

150

°C

6

Weight

FC

20

mounting force with clip

d Spp/App

VISOL

t = 1 minute

Product Marking

UL

Logo

IXYS

mm

terminal to backside

5.1

mm

3000

V

2500

V

50/60 Hz, RMS; IISOL ≤ 1 mA

Part description

C

L

A

40

P

1200

FC

®

ISOPLUS®

Part Number

N

1.7

t = 1 second

isolation voltage

120

terminal to terminal

creepage distance on surface | striking distance through air

d Spb/Apb

g

=

=

=

=

=

=

=

Thyristor (SCR)

High Efficiency Thyristor

(up to 1200V)

Current Rating [A]

Phase leg

Reverse Voltage [V]

i4-Pac (5)

XXXXXXXXX

Date Code

yywwZ

1234

Location

Lot#

Ordering

Standard

Ordering Number

CLA40P1200FC

Equivalent Circuits for Simulation

I

V0

R0

Marking on Product

CLA40P1200FC

* on die level

Delivery Mode

Tube

Code No.

510210

T VJ = 150°C

Thyristor

V 0 max

threshold voltage

0.86

V

R0 max

slope resistance *

5.4

mΩ

IXYS reserves the right to change limits, conditions and dimensions.

© 2019 IXYS all rights reserved

Quantity

25

Data according to IEC 60747and per semiconductor unless otherwise specified

20191202d

�CLA40P1200FC

Outlines i4-Pac

D2

A

A2

E1

L

L1

D

D3

D1

R

Q

E

4x e

c

1 2 3 4 5

4x b2

5x b

A1

b4

W

Dim.

A

A1

A2

b

b2

b4

c

D

D1

D2

D3

E

E1

e

L

L1

Q

R

W

Millimeter

min

max

4.83

5.21

2.59

3.00

1.17

2.16

1.14

1.40

1.47

1.73

2.54

2.79

0.51

0.74

20.80

21.34

14.99

15.75

1.65

2.03

20.30

20.70

19.56

20.29

16.76

17.53

3.81 BSC

19.81

21.34

2.11

2.59

5.33

6.20

4.57

2.54

0.10

-

Inches

min

max

0.190

0.205

0.102

0.118

0.046

0.085

0.045

0.055

0.058

0.068

0.100

0.110

0.020

0.029

0.819

0.840

0.590

0.620

0.065

0.080

0.799

0.815

0.770

0.799

0.660

0.690

0.150 BSC

0.780

0.840

0.083

0.102

0.210

0.244

0.100

0.180

0.004

-

Die konvexe Form des Substrates ist typ. < 0.05 mm über

der Kunststoffoberfläche der Bauteilunterseite

The convexbow of substrate is typ. < 0.05 mm over plastic

surface level ofdevice bottom side

2

IXYS reserves the right to change limits, conditions and dimensions.

© 2019 IXYS all rights reserved

1

4

5

3

Data according to IEC 60747and per semiconductor unless otherwise specified

20191202d

�CLA40P1200FC

Thyristor

150

600

120

500

IT 90

ITSM 400

[A] 60

10000

TVJ = 45°C

TVJ = 125°C

[A2s]

1,0

50 Hz, 80% VRRM

1,5

2,0

2,5

0,01

100

0,1

VT [V]

1

1

Fig. 3 I t versus time (1-10 s)

1000

80

70

2: IGT, TVJ = 25°C

3: IGT, TVJ = -40°C

1

50

tgd

IT(AV)M

[µs]

[A]

40

6

4

5

10

lim.

1000

10000

[W]

0

40

RthHA

0.6

0.8

1.0

2.0

4.0

8.0

80

120

160

Tcase [°C]

Fig. 5 Gate controlled delay time tgd

dc =

1

0.5

0.4

0.33

0.17

0.08

40

1000

IG [mA]

Fig. 4 Gate voltage & gate current

P(AV)

0

100

IG [mA]

60

10

typ.

1

10

0,1

100

30

20

4: PGAV = 0.5 W

5: PGM = 1 W

6: PGM = 10 W

10

dc =

1

0.5

0.4

0.33

0.17

0.08

60

TVJ = 125°C

100

23

1

4 5 6 7 8 910

t [ms]

1: IGD, TVJ = 150°C

1

3

2

Fig. 2 Surge overload current

ITSM: crest value, t: duration

10

[V]

2

t [s]

Fig. 1 Forward characteristics

VG

TVJ = 125°C

200

100

0,5

TVJ = 45°C

1000

TVJ = 125°C

TVJ = 25°C

0

0,0

2

It

[A] 300

30

VR = 0 V

Fig. 6 Max. forward current at

case temperature

0,8

0,6

ZthJC

0,4

i Rthi (K/W)

1

0.01

2

005

3

0.17

4

0.36

5

0.21

[K/W]

20

0,2

0

ti (s)

0.0004

0.009

0.014

0.05

0.36

0,0

0

10

20

30

40

IT(AV) [A]

50 0

50

100

150

Fig. 7a Power dissipation versus direct output current

Fig. 7b and ambient temperature

IXYS reserves the right to change limits, conditions and dimensions.

© 2019 IXYS all rights reserved

1

10

100

1000

10000

t [ms]

Tamb [°C]

Fig. 7 Transient thermal impedance junction to case

Data according to IEC 60747and per semiconductor unless otherwise specified

20191202d

�

很抱歉,暂时无法提供与“CLA40P1200FC”相匹配的价格&库存,您可以联系我们找货

免费人工找货