Si52143

PCI-E XPRESS G EN 1, G EN 2, & G EN 3 Q UAD O UTPUT

C L O C K G ENERATOR WITH 2 5 M H Z R E F E R E N C E C L O C K

Features

Ordering Information:

See page 18

Applications

Functional Block Diagram

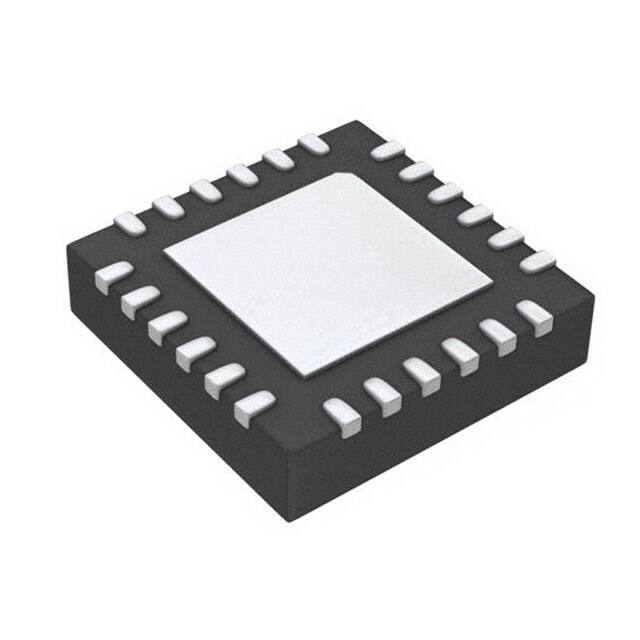

23

22

21

20

19

VDD_REF

1

1

18 OE[3:2]

REF

2

17 VDD_DIFF

SSON2

3

VSS_REF

4

1

OE_REF

5

VDD_DIFF

6

16 DIFF3

25

GND

15 DIFF3

14 DIFF2

13 DIFF2

7

8

9

10

11

12

VDD_DIFF

The Si52143 is a spread-spectrum enabled PCIe clock generator that can source

four PCIe clocks and a 25 MHz reference clock. The device has three hardware

output enable pins for enabling the outputs (on the fly while powered on), and one

hardware pin to control spread spectrum on PCIe clock outputs. In addition to the

hardware control pins, I2C programmability is also available to dynamically control

skew, edge rate and amplitude on the true, compliment, or both differential signals

on the PCIe clock outputs. This control feature enables optimal signal integrity as

well as optimal EMI signature on the PCIe clock outputs. Refer to AN636 for

signal integrity tuning and configurability. Measuring PCIe clock jitter is quick and

easy with the Silicon Labs PCIe Clock Jitter Tool. Download it for free at

www.silabs.com/pcie-learningcenter.

24

SCLK

Description

VDD_CORE

Wireless access point

Routers

SDATA

Network attached storage

Multi-function printer

DIFF1

Pin Assignments

XOUT

DIFF1

I2C support with readback

capabilities

Triangular spread spectrum profile

for maximum electromagnetic

interference (EMI) reduction

Industrial temperature

–40 to 85 °C

3.3 V power supply

24-pin QFN package

XIN/CLKIN

DIFF0

Four PCI-Express clocks

25 MHz reference clock output

25 MHz crystal input or clock input

Signal integrity tuning

VSS_CORE

DIFF0

PCI-Express Gen 1, Gen 2, Gen 3,

and Gen 4 common clock compliant

Gen 3 SRNS Compliant

Supports Serial ATA (SATA) at

100 MHz

Low power, push-pull HCSL

compatible differential outputs

No termination resistors required

Dedicated output enable hardware

pins for each clock output

Spread enable pin on differential

clocks

OE[1:0]1

Notes:

1. Internal 100 kohm pull-up.

2. Internal 100 kohm pull-down.

Patents pending

REF

XIN/CLKIN

XOUT

DIFF0

DIFF1

PLL

(SSC)

Divider

DIFF2

DIFF3

SCLK

SDATA

Control & Memory

OE_REF

OE [1:0]

Control

RAM

OE [3:2]

SSON

Rev 1.4 4/16

Copyright © 2016 by Silicon Laboratories

Si52143

�Si52143

2

Rev 1.4

�Si52143

TABLE O F C ONTENTS

Section

Page

1. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

2.1. Crystal Recommendations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

2.2. OE Pin Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

2.3. OE Assertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

2.4. OE Deassertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

2.5. SSON Pin Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

3. Test and Measurement Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4. Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4.1. I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2. Data Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

5. Pin Descriptions: 24-Pin QFN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6. Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7. Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

8. Land Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Rev 1.4

3

�Si52143

1. Electrical Specifications

Table 1. DC Electrical Specifications

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

3.3 V Operating Voltage

VDD core

3.3 ± 5%

3.135

3.3

3.465

V

3.3 V Input High Voltage

VIH

Control input pins

2.0

—

VDD + 0.3

V

3.3 V Input Low Voltage

VIL

Control input pins

VSS –

0.3

—

0.8

V

Input High Voltage

VIHI2C

SDATA, SCLK

2.2

—

—

V

Input Low Voltage

VILI2C

SDATA, SCLK

—

—

1.0

V

Input High Leakage Current

IIH

Except internal pull-down

resistors, 0 < VIN < VDD

—

—

5

A

Input Low Leakage Current

IIL

Except internal pull-up resistors, 0 < VIN < VDD

–5

—

—

A

3.3 V Output High Voltage

(Single-Ended Outputs)

VOH

IOH = –1 mA

2.4

—

—

V

3.3 V Output High Voltage

(Single-Ended Outputs)

VOL

IOL = 1 mA

–

—

0.4

V

High-impedance Output Current

IOZ

–10

—

10

µA

Input Pin Capacitance

CIN

1.5

—

5

pF

COUT

—

—

6

pF

LIN

—

—

7

nH

—

—

55

mA

Output Pin Capacitance

Pin Inductance

Dynamic Supply Current

4

IDD_3.3V

All outputs enabled. Differential clocks with 5” traces

and 2 pF load.

Rev 1.4

�Si52143

Table 2. AC Electrical Specification

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

LACC

Measured at VDD/2 differential

—

—

250

ppm

TDC

Measured at VDD/2

45

—

55

%

CLKIN Rising and Falling Slew

Rate

TR/TF

Measured between 0.2 VDD and

0.8 VDD

0.5

—

4.0

V/ns

Cycle to Cycle Jitter

TCCJ

Measured at VDD/2

—

—

250

ps

Long Term Jitter

TLTJ

Measured at VDD/2

—

—

350

ps

Input High Voltage

VIH

XIN/CLKIN pin

2

—

VDD+0.3

V

Input Low Voltage

VIL

XIN/CLKIN pin

—

—

0.8

V

Input High Current

IIH

XIN/CLKIN pin, VIN = VDD

—

—

35

µA

Input Low Current

IIL

XIN/CLKIN pin, 0 < VIN

很抱歉,暂时无法提供与“SI52143-A01AGMR”相匹配的价格&库存,您可以联系我们找货

免费人工找货